## General Description

The SI8600AC-B-IS devices are low-power bidirectional isolators compatible with the I<sup>2</sup>C interface. These devices have logic input and output buffers that are separated by using a silicon dioxide (SiO<sub>2</sub>) barrier. These devices block high voltages and prevent noise currents from entering the control side ground, avoiding circuit interference, and damaging sensitive components.

The SI8600AC-B-IS device is based on **iDivide®** technology with functional, performance, size, and power consumption advantages as compared to optocouplers.

The SI8600AC-B-IS provide two bidirectional channels, supporting a complete isolated I<sup>2</sup>C interface. The SI8600AC-B-IS is used in applications that have a single master. This device feature independent 3.0V supplies on each side of the isolator. These devices operate from DC to 2MHz at ambient temperatures of -40°C to +125°C

## Features

- Bidirectional I<sup>2</sup>C communication

- Ultra-low power consumption

- Supports up to 2MHz operation

- Open-drain interfaces

- Side 1 outputs with 3.5mA sink current

- Side 2 outputs with 35mA sink current

- 3.0V to 5.5V supply/logic levels

- High common-mode transient immunity: 120kV/μs

- typical RoHS-compliant, SOP-8

## Applications

- Isolated I<sup>2</sup>C, SMBus, PMBus

- interfaces Multilevel I<sup>2</sup>C interfaces

- Electric and Hybrid-Electric

- Vehicles Open-Drain Networks

- I<sup>2</sup>C Level Shifting

- Power supplies

## Ordering Guide

Table 1. Ordering guide

| Model Name <sup>1</sup> | Temperature Range | Total signal channel amount | No. of Bi-directional channels | Isolation Rating (kV rms) | Package | MSL Peak Temp <sup>2</sup> | Quantity per reel |

|-------------------------|-------------------|-----------------------------|--------------------------------|---------------------------|---------|----------------------------|-------------------|

| SI8600AC-B-IS           | -40 ~125°C        | 2                           | 2                              | 3                         | SOP-8   | Level-2-260C-1 YEAR        | 4000              |

<sup>1</sup>. PAI2xxxx is equals to PI2xxxx in the customer BOM. Devices with Q suffix are AEC-Q100 qualified.

<sup>2</sup>. MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

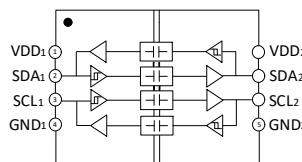

## Functional Block Diagrams

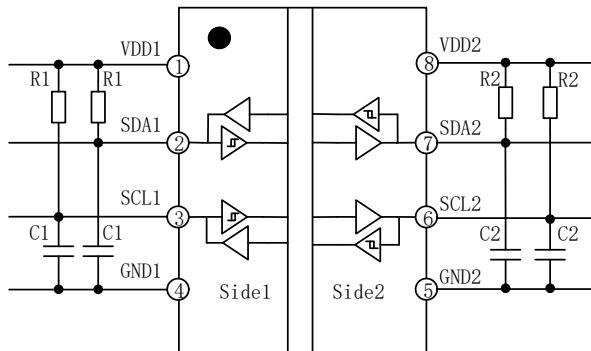

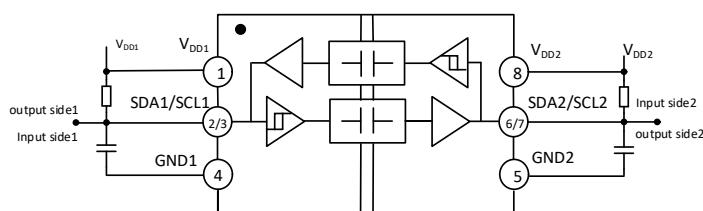

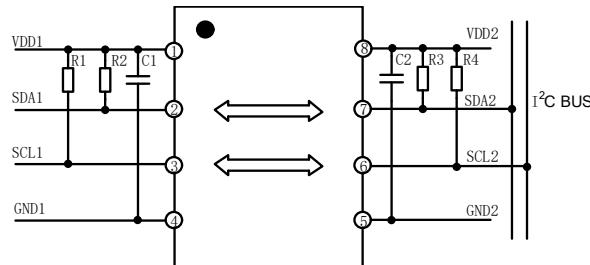

Figure 1. Functional Block Diagram

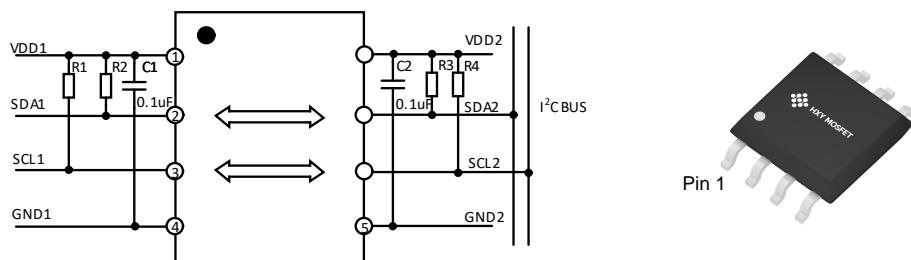

Figure 2. Typical Application Circuit

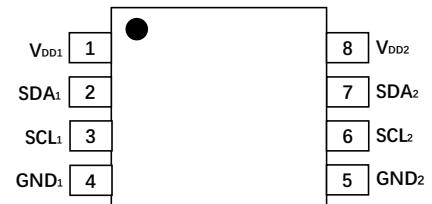

## Pin Configurations And Functions

Table 2. Pin Function Descriptions

| Pin No. | Name             | Description                                                     |

|---------|------------------|-----------------------------------------------------------------|

| 1       | V <sub>DD1</sub> | Supply Voltage for Isolator Side 1.                             |

| 2       | SDA <sub>1</sub> | Serial data input / output, side 1.                             |

| 3       | SCL <sub>1</sub> | Serial clock input / output, side 1.                            |

| 4       | GND <sub>1</sub> | Ground 1. This pin is the ground reference for Isolator Side 1. |

| 5       | GND <sub>2</sub> | Ground 2. This pin is the ground reference for Isolator Side 2. |

| 6       | SCL <sub>2</sub> | Serial clock input / output, side 2.                            |

| 7       | SDA <sub>2</sub> | Serial data input / output, side 2.                             |

| 8       | V <sub>DD2</sub> | Supply Voltage for Isolator Side 2.                             |

Figure 3. Pin Configuration

## Absolute Maximum Ratings

T<sub>A</sub> = 25°C, unless otherwise noted.

Table 3. Absolute Maximum Ratings<sup>4</sup>

| Parameter                                                                                  | Rating                             |

|--------------------------------------------------------------------------------------------|------------------------------------|

| Supply Voltages (V <sub>DD1</sub> -GND <sub>1</sub> , V <sub>DD2</sub> -GND <sub>2</sub> ) | -0.5 V to +7.0 V                   |

| Signal Voltage SDA1/SCL1                                                                   | -0.5 V to V <sub>DDX</sub> + 0.5 V |

| Signal Voltage SDA2/SCL2                                                                   | -0.5 V to V <sub>DDX</sub> + 0.5 V |

| Average Output Current SDA1/SCL1 (I <sub>O1</sub> )                                        | -20 mA to +20 mA                   |

| Average Output Current SDA2/SCL2 (I <sub>O2</sub> )                                        | -100 mA to +100 mA                 |

| Storage Temperature (T <sub>ST</sub> ) Range                                               | -65°C to +150°C                    |

| Maximum junction temperature T <sub>J(MAX)</sub>                                           | +150°C                             |

Notes:

1. All voltage values here within are with respect to the local ground pin (GND1 or GND2) and are peak voltage values.

2. Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

## Recommended Operating Conditions

Table 4. Recommended Operating Conditions

| Parameter                                                                                                    | Symbol             | Min                  | Typ | Max                           | Unit |

|--------------------------------------------------------------------------------------------------------------|--------------------|----------------------|-----|-------------------------------|------|

| Supply Voltage                                                                                               | V <sub>DDX</sub> 1 | 3                    |     | 5.5                           | V    |

| Input/Output Signal Voltage (V <sub>SDA1</sub> , V <sub>SCL1</sub> , V <sub>SDA2</sub> , V <sub>SCL2</sub> ) |                    | 0                    |     | V <sub>DDX</sub> <sup>1</sup> | V    |

| Low-level input voltage, side 1                                                                              | V <sub>IL1</sub>   | 0                    |     | 0.47                          | V    |

| High-level input voltage, side 1                                                                             | V <sub>IH1</sub>   | 0.7*V <sub>DD1</sub> |     | V <sub>DD1</sub>              | V    |

| Low-level input voltage, side 2                                                                              | V <sub>IL2</sub>   | 0                    |     | 0.3*V <sub>DD2</sub>          | V    |

| High-level input voltage, side 2                                                                             | V <sub>IH2</sub>   | 0.7*V <sub>DD2</sub> |     | V <sub>DD2</sub>              | V    |

| Output current, side 1                                                                                       | I <sub>OL1</sub>   | 0.5                  |     | 3.5                           | mA   |

| Output current, side 2                                                                                       | I <sub>OL2</sub>   | 0.5                  |     | 35                            | mA   |

| Capacitive load, side 1                                                                                      | C <sub>1</sub>     |                      |     | 40                            | pF   |

| Capacitive load, side 2                                                                                      | C <sub>2</sub>     |                      |     | 400                           | pF   |

| Operating frequency                                                                                          | f <sub>MAX</sub>   |                      |     | 2                             | MHz  |

| Ambient Operating Temperature                                                                                | T <sub>A</sub>     | -40                  |     | 125                           | °C   |

Notes:

<sup>1</sup> V<sub>DDX</sub> is the side voltage power supply V<sub>DD</sub>, where x = 1 or 2.

## Truth Tables

Table 5. Truth Table

| <b>V<sub>lx</sub> Input<sup>1</sup></b> | <b>V<sub>DDI</sub> State<sup>1</sup></b> | <b>V<sub>DDO</sub> State<sup>1</sup></b> | <b>V<sub>ox</sub> Output<sup>1</sup></b> |

|-----------------------------------------|------------------------------------------|------------------------------------------|------------------------------------------|

| Low                                     | Powered <sup>2</sup>                     | Powered <sup>2</sup>                     | Low                                      |

| High                                    | Powered <sup>2</sup>                     | Powered <sup>2</sup>                     | High Impedance                           |

| Open <sup>4</sup>                       | Powered <sup>2</sup>                     | Powered <sup>2</sup>                     | High Impedance                           |

| Don't Care                              | Unpowered <sup>3</sup>                   | Powered <sup>2</sup>                     | High Impedance                           |

| Don't Care                              | Powered <sup>2</sup>                     | Unpowered <sup>3</sup>                   | High Impedance                           |

Notes:

<sup>1</sup> V<sub>lx</sub>/V<sub>ox</sub> are the input/output signals of a given channel (SDA or SCL). V<sub>DDI</sub>/V<sub>DDO</sub> are the supply voltages on the input/output signal sides of this given channel. <sup>2</sup> Powered means V<sub>DDX</sub> ≥ 2.95V

<sup>3</sup> Unpowered means V<sub>DDX</sub> < 2.30V

<sup>4</sup> Invalid input condition as an I<sup>2</sup>C system requires that a pullup resistor to V<sub>DD</sub> is connected.

## Specifications

### Electrical Characteristics

Table 6. DC Specifications

V<sub>DD1</sub> - V<sub>GND1</sub> = V<sub>DD2</sub> - V<sub>GND2</sub> = 3.0V ~ 5.5V, typical value is measured at T<sub>A</sub>=25°C, unless otherwise noted.

| Parameter                                                                                                        | Symbol                           | Min                    | Typ                    | Max                    | Unit | Test Conditions/Comments                                                                                            |

|------------------------------------------------------------------------------------------------------------------|----------------------------------|------------------------|------------------------|------------------------|------|---------------------------------------------------------------------------------------------------------------------|

| <b>Side 1 Logic Levels</b>                                                                                       |                                  |                        |                        |                        |      |                                                                                                                     |

| Voltage input threshold low, SDA <sub>1</sub> and SCL <sub>1</sub>                                               | V <sub>I LT1</sub>               | 470                    | 510                    | 570                    | mV   |                                                                                                                     |

| Voltage input threshold high, SDA <sub>1</sub> and SCL <sub>1</sub>                                              | V <sub>I HT1</sub>               | 540                    | 580                    | 630                    | mV   |                                                                                                                     |

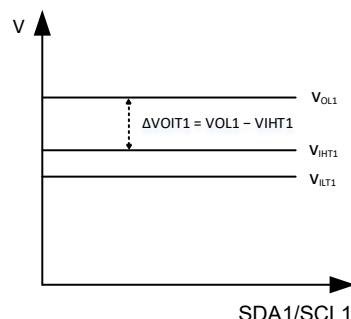

| Voltage input hysteresis                                                                                         | V <sub>HYST1</sub>               | 30                     | 70                     |                        | mV   | V <sub>I HT1</sub> - V <sub>I LT1</sub>                                                                             |

| Low-level output voltage, SDA <sub>1</sub> and SCL <sub>1</sub>                                                  | V <sub>OL1</sub>                 | 650                    | 720                    | 800                    | mV   | 0.5 mA ≤ (IsDA <sub>1</sub> and IsCL <sub>1</sub> ) ≤ 3.5 mA                                                        |

| Low-level output voltage to high-level input voltage threshold difference, SDA <sub>1</sub> and SCL <sub>1</sub> | ΔV <sub>O LT1</sub> <sup>1</sup> | 60                     | 120                    |                        | mV   | 0.5 mA ≤ (IsDA <sub>1</sub> and IsCL <sub>1</sub> ) ≤ 3.5 mA                                                        |

| <b>Side 2 Logic Levels</b>                                                                                       |                                  |                        |                        |                        |      |                                                                                                                     |

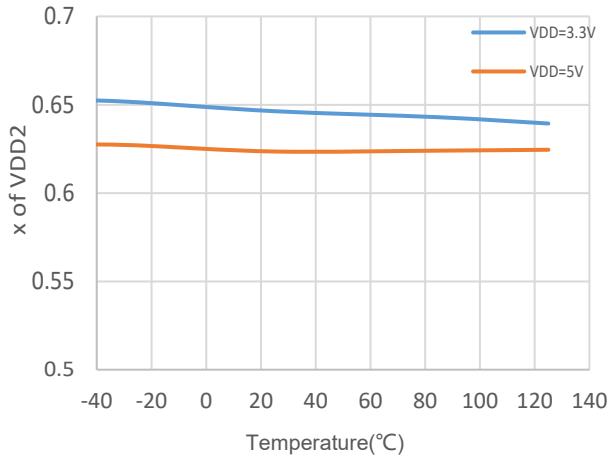

| Voltage input threshold low, SDA <sub>2</sub> and SCL <sub>2</sub>                                               | V <sub>I LT2</sub>               | 0.30* V <sub>DD2</sub> |                        | 0.42* V <sub>DD2</sub> | V    |                                                                                                                     |

| Voltage input threshold high, SDA <sub>2</sub> and SCL <sub>2</sub>                                              | V <sub>I HT2</sub>               | 0.58* V <sub>DD2</sub> |                        | 0.69* V <sub>DD2</sub> | V    |                                                                                                                     |

| Voltage input hysteresis                                                                                         | V <sub>HYST2</sub>               | 0.15* V <sub>DD2</sub> | 0.28* V <sub>DD2</sub> |                        | V    | V <sub>I HT2</sub> - V <sub>I LT2</sub>                                                                             |

| Low-level output voltage, SDA <sub>2</sub> and SCL <sub>2</sub>                                                  | V <sub>OL2</sub>                 |                        |                        | 0.4                    | V    | 0.5 mA ≤ (IsDA <sub>2</sub> and IsCL <sub>2</sub> ) ≤ 35 mA                                                         |

| <b>Both Sides</b>                                                                                                |                                  |                        |                        |                        |      |                                                                                                                     |

| Input leakage currents, SDA <sub>1</sub> , SCL <sub>1</sub> , SDA <sub>2</sub> , and SCL <sub>2</sub>            | I <sub>IN</sub>                  |                        | 0.01                   | 10                     | μA   | V <sub>SDA1</sub> , V <sub>SCL1</sub> = V <sub>DD1</sub> ; V <sub>SDA2</sub> , V <sub>SCL2</sub> = V <sub>DD2</sub> |

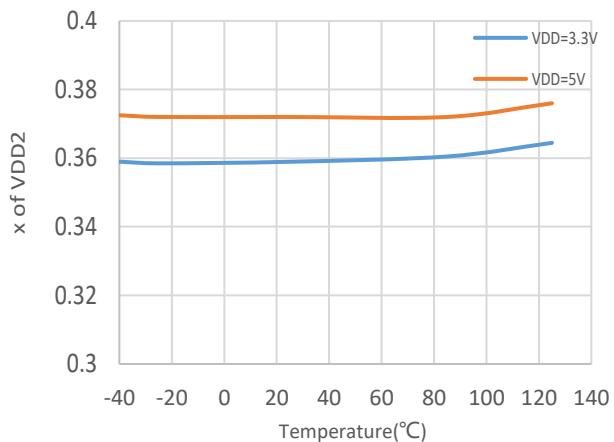

| V <sub>DDX</sub> <sup>3</sup> Undervoltage Rising Threshold                                                      | V <sub>DDX UV+</sub>             | 2.45                   | 2.75                   | 2.95                   | V    |                                                                                                                     |

| V <sub>DDX</sub> <sup>3</sup> Undervoltage Falling Threshold                                                     | V <sub>DDX UV-</sub>             | 2.30                   | 2.60                   | 2.80                   | V    |                                                                                                                     |

| V <sub>DDX</sub> <sup>3</sup> Hysteresis                                                                         | V <sub>DDX UVH</sub>             |                        | 0.15                   |                        | V    |                                                                                                                     |

Notes:

1. ΔV<sub>O LT1</sub> = V<sub>OL1</sub> - V<sub>I HT1</sub>. This is the minimum difference between the output logic low level and the input logic threshold within a given component. This ensures that there is no possibility of the part latching up the bus to which it is connected.

2. V<sub>DDX</sub> is the side voltage power supply VDD, where x = 1 or 2.

Table 7. Quiescent Supply Current

$V_{DD1} - V_{GND1} = V_{DD2} - V_{GND2} = 3.0V \sim 5.5V$ , typical value is measured at  $T_A=25^\circ C$ , unless otherwise noted.

| Part          | Symbol               | Min | Typ | Max | Unit | Test Conditions    |                             |

|---------------|----------------------|-----|-----|-----|------|--------------------|-----------------------------|

|               |                      |     |     |     |      | Supply voltage     | Input signal                |

| SI8600AC-B-IS | I <sub>DD1 (Q)</sub> |     | 1.7 | 2.4 | mA   | 5V <sub>DC</sub>   | All IO = 0V <sub>DC</sub>   |

|               | I <sub>DD2 (Q)</sub> |     | 1.4 | 2.1 | mA   |                    | All IO = 5V <sub>DC</sub>   |

|               | I <sub>DD1 (Q)</sub> |     | 1.5 | 2.3 | mA   |                    | All IO = 0V <sub>DC</sub>   |

|               | I <sub>DD2 (Q)</sub> |     | 1.2 | 1.8 | mA   |                    | All IO = 3.3V <sub>DC</sub> |

|               | I <sub>DD1 (Q)</sub> |     | 1.5 | 2.3 | mA   | 3.3V <sub>DC</sub> | All IO = 0V <sub>DC</sub>   |

|               | I <sub>DD2 (Q)</sub> |     | 1.2 | 1.8 | mA   |                    | All IO = 5V <sub>DC</sub>   |

|               | I <sub>DD1 (Q)</sub> |     | 1.5 | 2.3 | mA   |                    | All IO = 3.3V <sub>DC</sub> |

|               | I <sub>DD2 (Q)</sub> |     | 1.2 | 1.8 | mA   |                    | All IO = 0V <sub>DC</sub>   |

Table 8. Switching Specifications

$V_{DD1} - V_{GND1} = V_{DD2} - V_{GND2} = 3.0V \sim 5.5V$ , typical value is measured at  $T_A=25^\circ C$ , unless otherwise noted.

| Parameter                                                         | Symbol              | Min | Typ | Max | Unit  | Test Conditions/Comments                                                                                           |  |

|-------------------------------------------------------------------|---------------------|-----|-----|-----|-------|--------------------------------------------------------------------------------------------------------------------|--|

| Output Signal Fall Time SDA1, SCL1                                | t <sub>f1</sub>     | 10  | 18  | 32  | ns    | 0.9 × V <sub>DD1</sub> to 0.9V; R1 = 1500Ω, C1 = 40pF, @ 5V <sub>DC</sub> supply                                   |  |

|                                                                   |                     | 8   | 16  | 30  | ns    | R1 = 1000Ω, C1 = 40pF; @ 3.3V <sub>DC</sub> supply                                                                 |  |

| Output Signal Fall Time SDA2, SCL2                                | t <sub>f2</sub>     | 20  | 36  | 60  | ns    | 0.9 × V <sub>DD2</sub> to 0.4V; R2 = 150Ω, C2 = 400pF, @ 5V <sub>DC</sub> supply                                   |  |

|                                                                   |                     | 18  | 31  | 57  | ns    | R2 = 100Ω, C2 = 400pF; @ 3.3V <sub>DC</sub> supply                                                                 |  |

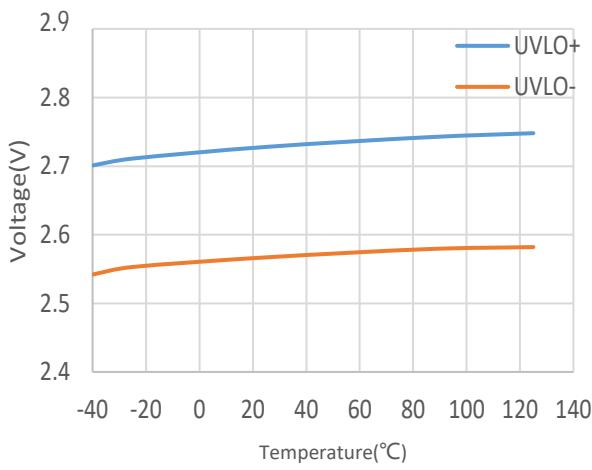

| Low-to-High Propagation Delay, Side 1 to Side 2                   | t <sub>pLH1-2</sub> |     | 45  | 68  | ns    | 0.55V to 0.7 × V <sub>DD2</sub> ; R1 = 1500Ω, R2 = 150Ω, C1, C2 = 10 pF; @ 5V <sub>DC</sub> supply                 |  |

|                                                                   |                     |     | 38  | 63  | ns    | R1 = 1000Ω, R2 = 100Ω, C1, C2 = 10pF; @ 3.3V <sub>DC</sub> supply                                                  |  |

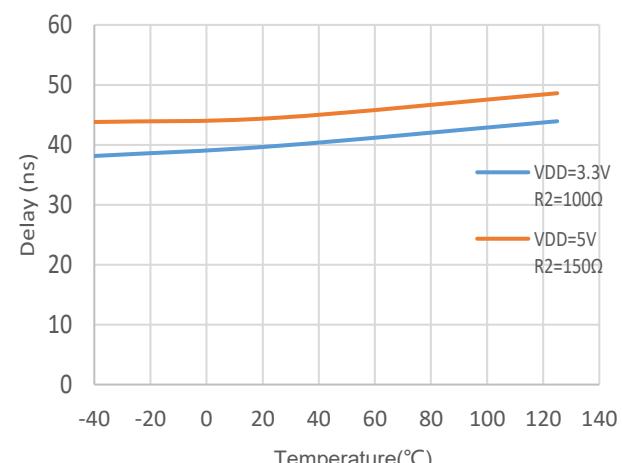

| High-to-Low Propagation Delay, Side 1 to Side 2                   | t <sub>PHL1-2</sub> |     | 67  | 130 | ns    | 0.7V to 0.4V; R1 = 1500Ω, R2 = 150Ω, C1, C2 = 10pF; @ 5V <sub>DC</sub> supply                                      |  |

|                                                                   |                     |     | 64  | 130 | ns    | R1 = 1000Ω, R2 = 100Ω, C1, C2 = 10pF; @ 3.3V <sub>DC</sub> supply                                                  |  |

| Pulse Width Distortion  t <sub>pHL1-2</sub> - t <sub>pLH1-2</sub> | PWD <sub>1-2</sub>  |     | 22  | 60  | ns    | R1 = 1500Ω, R2 = 150Ω, C1, C2 = 10pF; @ 5V <sub>DC</sub> supply                                                    |  |

|                                                                   |                     |     | 26  | 65  | ns    | R1 = 1000Ω, R2 = 100Ω, C1, C2 = 10pF; @ 3.3V <sub>DC</sub> supply                                                  |  |

| Low-to-High Propagation Delay, Side 2 to Side 1                   | t <sub>pLH2-1</sub> |     | 62  | 80  | ns    | 0.4 × V <sub>DD2</sub> to 0.7 × V <sub>DD1</sub> ; R1 = 1500Ω, R2 = 150Ω, C1, C2 = 10pF; @ 5V <sub>DC</sub> supply |  |

|                                                                   |                     |     | 50  | 70  | ns    | R1 = 1000Ω, R2 = 100Ω, C1, C2 = 10pF; @ 3.3V <sub>DC</sub> supply                                                  |  |

| High-to-Low Propagation Delay, Side 2 to Side 1                   | t <sub>PHL2-1</sub> |     | 54  | 84  | ns    | 0.4 × V <sub>DD2</sub> to 0.9V; R1 = 1500Ω, R2 = 150Ω, C1, C2 = 10pF; @ 5V <sub>DC</sub> supply                    |  |

|                                                                   |                     |     | 56  | 86  | ns    | R1 = 1000Ω, R2 = 100Ω, C1, C2 = 10pF; @ 3.3V <sub>DC</sub> supply                                                  |  |

| Pulse Width Distortion  t <sub>pHL2-1</sub> - t <sub>pLH2-1</sub> | PWD <sub>2-1</sub>  |     | 12  | 25  | ns    | R1 = 1500Ω, R2 = 150Ω, C1, C2 = 10pF; @ 5V <sub>DC</sub> supply                                                    |  |

|                                                                   |                     |     | 15  | 35  | ns    | R1 = 1000Ω, R2 = 100Ω, C1, C2 = 10pF; @ 3.3V <sub>DC</sub> supply                                                  |  |

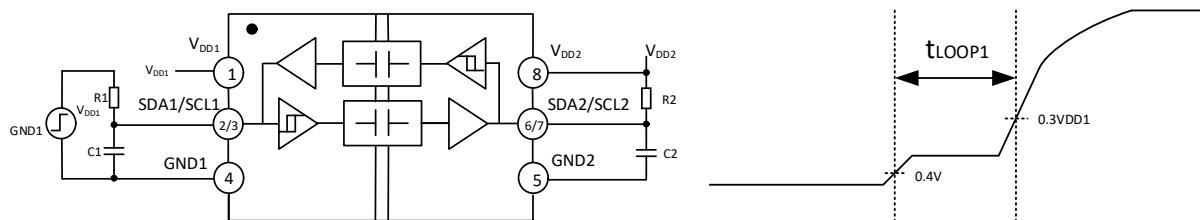

| Round-trip propagation delay on Side 1                            | t <sub>LOOP1</sub>  |     | 116 | 180 | ns    | 0.4 V to 0.3 × V <sub>DD1</sub> ; R1 = 1500Ω, R2 = 150Ω, C1, C2 = 10pF; @ 5V <sub>DC</sub> supply                  |  |

|                                                                   |                     |     | 98  | 162 | ns    | R1 = 1000Ω, R2 = 100Ω, C1, C2 = 10pF; @ 3.3V <sub>DC</sub> supply                                                  |  |

| Common-Mode Transient Immunity <sup>2</sup>                       | CMTI                |     | 120 |     | kV/μs | $V_{IN} = V_{DDx}^1$ or 0V, $V_{CM} = 1000$ V.                                                                     |  |

| ESD (HBM - Human body model)                                      | ESD                 |     | ±6  |     | kV    |                                                                                                                    |  |

## Insulation And Safety Related Specifications

Table 9. Insulation Specifications

| Parameter                                        | Symbol            | Value | Unit             | Test Conditions/Comments                                                             |

|--------------------------------------------------|-------------------|-------|------------------|--------------------------------------------------------------------------------------|

| Rated Dielectric Insulation Voltage              | V <sub>I</sub> so | 3000  | V <sub>RMS</sub> | 1-minute duration, certificated                                                      |

| Minimum External Air Gap (Clearance)             | CLR               | ≥4.0  | mm               | Measured from input terminals to output terminals, shortest distance through air     |

| Minimum External Tracking (Creepage)             | CRP               | ≥4.0  | mm               | Measured from input terminals to output terminals, shortest distance path along body |

| Minimum Internal Gap (Internal Clearance)        | DTI               | ≥21   | μm               | Insulation distance through insulation                                               |

| Tracking Resistance (Comparative Tracking Index) | CTI               | ≥400  | V                | DIN EN 60112 (VDE 0303-11):2010-05                                                   |

| Material Group                                   |                   | II    |                  | IEC 60112:2003 + A1:2009                                                             |

## Package Characteristics

Table 10. Package Characteristics

| Parameter                                  | Symbol            | Value             | Unit | Test Conditions/Comments                      |

|--------------------------------------------|-------------------|-------------------|------|-----------------------------------------------|

| Resistance (Input to Output) <sup>1</sup>  | R <sub>I</sub> -O | ≥10 <sup>12</sup> | Ω    | V <sub>IO</sub> =500V, T <sub>A</sub> = 25°C  |

| Resistance (Input to Output) <sup>1</sup>  | R <sub>I</sub> -O | ≥10 <sup>11</sup> | Ω    | V <sub>IO</sub> =500V, T <sub>A</sub> = 125°C |

| Resistance (Input to Output) <sup>1</sup>  | R <sub>I</sub> -O | ≥10 <sup>9</sup>  | Ω    | V <sub>IO</sub> =500V, T <sub>A</sub> = 150°C |

| Capacitance (Input to Output) <sup>1</sup> | C <sub>I</sub> -O | 1.5               | pF   | @300kHz                                       |

| Input Capacitance <sup>2</sup>             | C <sub>I</sub>    | 3                 | pF   | @1MHz, ensured by design                      |

| IC Junction to Ambient Thermal Resistance  | θ <sub>JA</sub>   | 100               | °C/W |                                               |

Notes:

1. The device is considered a 2-terminal device. Short-circuit all terminals on the VDD<sub>1</sub> side as one terminal and short-circuit all terminals on the VDD<sub>2</sub> side as the other terminal.

2. Testing from the input signal pin to ground.

**DIN EN IEC 60747-17 (VDE 0884-17): 2021-10 Insulation Characteristics**

Table 11.VDE Insulation Characteristics

| Description                                              | Test Conditions/<br>Comments                                                                                            | Symbol             | Characteristic | Unit                                  |

|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--------------------|----------------|---------------------------------------|

| Installation Classification per DIN VDE 0110             |                                                                                                                         |                    |                |                                       |

| For Rated Mains Voltage $\leq 150$ V <sub>RMS</sub>      |                                                                                                                         |                    | I to IV        |                                       |

| For Rated Mains Voltage $\leq 300$ V <sub>RMS</sub>      |                                                                                                                         |                    | I to III       |                                       |

| For Rated Mains Voltage $\leq 400$ V <sub>RMS</sub>      |                                                                                                                         |                    | I to III       |                                       |

| Climatic Classification                                  |                                                                                                                         |                    | 40/125/21      |                                       |

| Pollution Degree per DIN VDE 0110, Table 1               |                                                                                                                         |                    | 2              |                                       |

| Maximum repetitive peak isolation voltage                | Time dependent dielectric breakdown test                                                                                | V <sub>IORM</sub>  | 707            | V <sub>peak</sub>                     |

| Maximum isolation working voltage                        | AC voltage (sine wave)<br>DC Voltage                                                                                    | V <sub>IOWM</sub>  | 500<br>707     | V <sub>RMS</sub><br>V <sub>peak</sub> |

| Input to Output Test Voltage, Method B1                  |                                                                                                                         |                    |                |                                       |

| 100% production test, no pre-condition tests             | $V_{IORM} \times 1.5 = V_{pd(m)}$ , $t_{ini} = t_m = 1$ sec, partial discharge $< 5$ pC                                 | V <sub>pd(m)</sub> | 1061           | V <sub>peak</sub>                     |

| Input to Output Test Voltage, Method A                   |                                                                                                                         |                    |                |                                       |

| After Environmental Tests Subgroup 1                     | $V_{IORM} \times 1.3 = V_{pd(m)}$ , $t_{ini} = 60$ sec, $t_m = 10$ sec, partial discharge $< 5$ pC                      | V <sub>pd(m)</sub> | 919            | V <sub>peak</sub>                     |

| After Input and/or Safety Test Subgroup 2 and Subgroup 3 | $V_{IORM} \times 1.2 = V_{pd(m)}$ , $t_{ini} = 60$ sec, $t_m = 10$ sec, partial discharge $< 5$ pC                      | V <sub>pd(m)</sub> | 848            | V <sub>peak</sub>                     |

| Highest Allowable Overvoltage                            | $V_{TEST} = V_{IOTM}$<br>$t = 60$ s (qualification);<br>$V_{TEST} = 1.2 \times V_{IOTM}$<br>$t = 1$ s (100% production) | V <sub>IOTM</sub>  | 4200           | V <sub>peak</sub>                     |

| Maximum Surge Isolation Voltage                          | Basic insulation, 1.2/50 $\mu$ s combination wave, $V_{TEST} = 1.3 \times V_{IOSM}$ (qualification) <sup>1</sup>        | V <sub>IOSM</sub>  | 5000           | V <sub>peak</sub>                     |

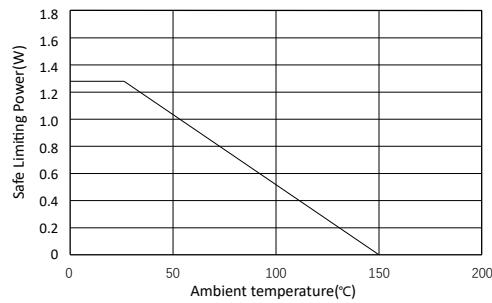

| Safety Limiting Values                                   | Maximum value allowed in the event of a failure (see Figure 4)                                                          |                    |                |                                       |

| Maximum Safety Temperature                               |                                                                                                                         | T <sub>S</sub>     | 150            | °C                                    |

| Maximum Power Dissipation at 25°C                        |                                                                                                                         | P <sub>S</sub>     | 1.25           | W                                     |

| Insulation Resistance                                    | $V_{IO} = 500$ V, $T_A = 25$ °C                                                                                         | R <sub>I-O</sub>   | $\geq 10^{12}$ | Ω                                     |

| Insulation Resistance                                    | $V_{IO} = 500$ V, $100$ °C $\leq T_A \leq 125$ °C                                                                       | R <sub>I-O</sub>   | $\geq 10^{11}$ | Ω                                     |

| Insulation Resistance at T <sub>S</sub>                  | $V_{IO} = 500$ V, $T_S = 150$ °C                                                                                        | R <sub>I-O</sub>   | $\geq 10^9$    | Ω                                     |

Notes:

<sup>1</sup>In accordance with DIN V VDE V 0884-17, SI8600AC-B-IS is proof tested by applying a surge isolation voltage of 6500V.

### Typical Thermal Characteristics

Figure 4. Thermal Derating Curve, Dependence Of Safety Limiting Values with Ambient Temperature per VDE

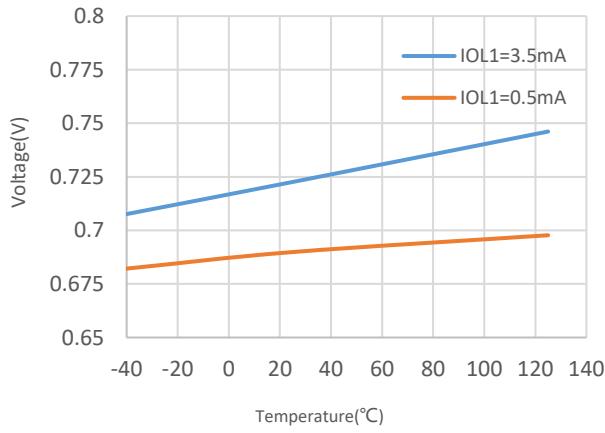

Figure 5. Side 1: Output Low Voltage vs Free-Air Temperature

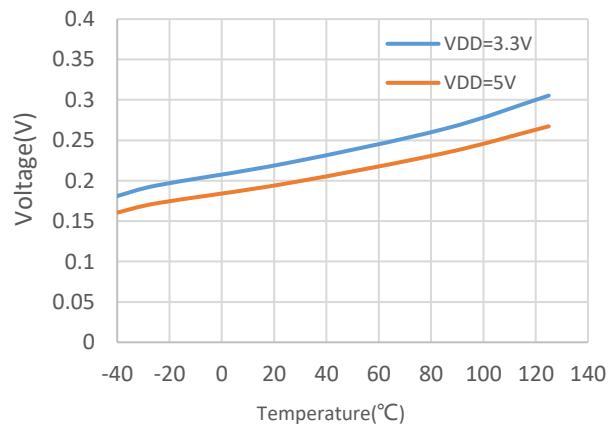

Figure 6. Side 2: Output Low Voltage vs Free-Air Temperature, Sink 35mA

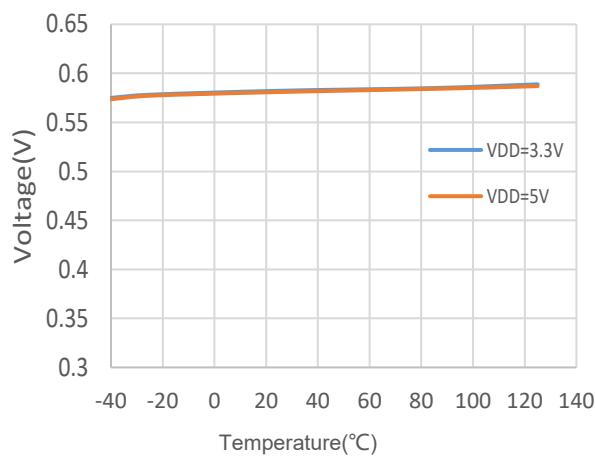

Figure 7. Side 1: Input Threshold High vs Free-Air Temperature

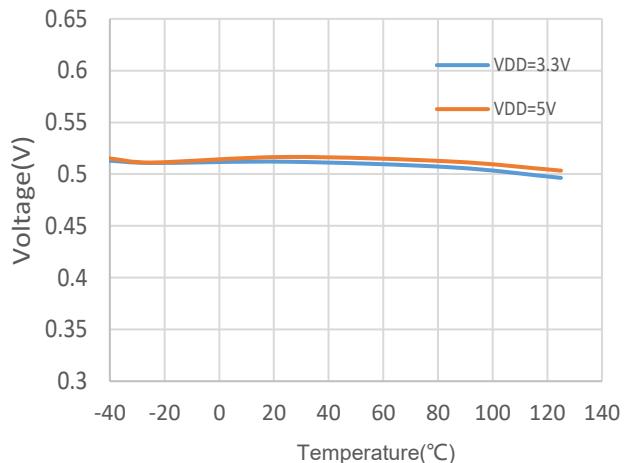

Figure 8. Side 1: Input Threshold Low vs Free-Air Temperature

Figure 9 . Side 2: Input Threshold High vs Free-Air Temperature

Figure 10. Side 2: Input Threshold Low vs Free-Air Temperature

Figure 11 UVLO vs Free-Air Temperature

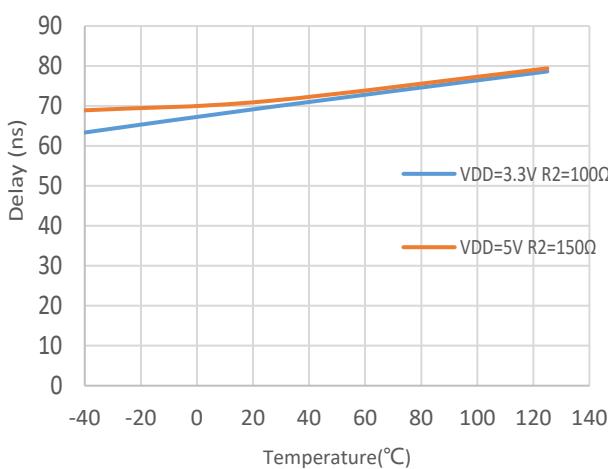

Figure 12. tPLH1-2 Propagation Delay vs Free-Air Temperature

Figure 13. tPLH1-2 Propagation Delay vs Free-Air Temperature

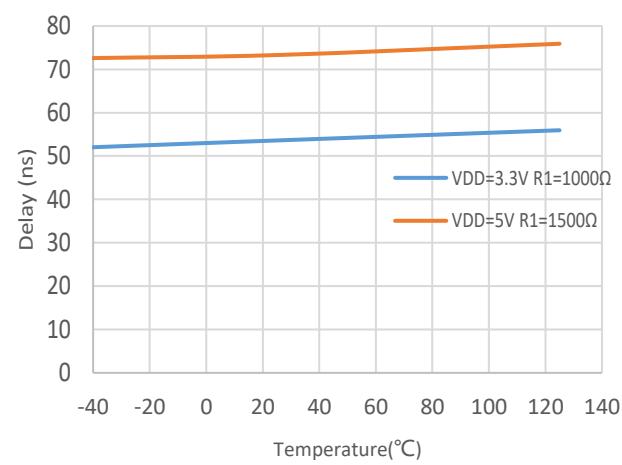

Figure 14. tPLH2-1 Propagation Delay vs Free-Air Temperature

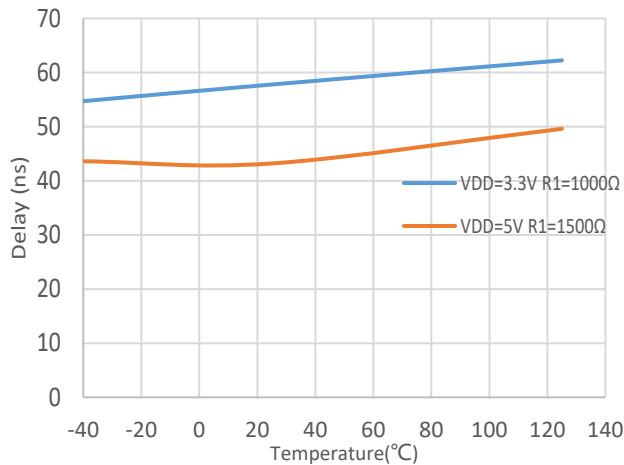

Figure 15.  $t_{PHL2-1}$  Propagation Delay vs Free-Air Temperature

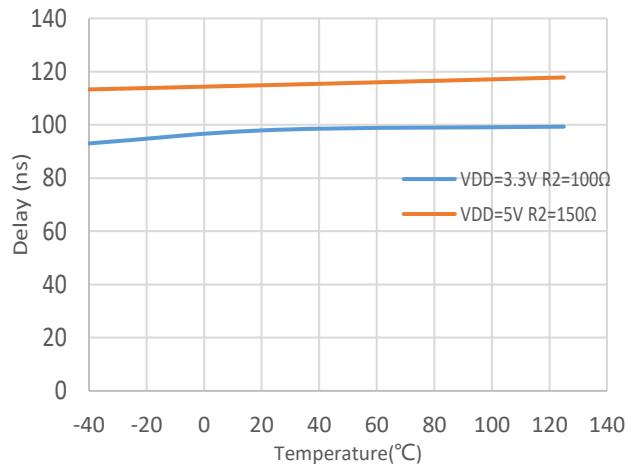

Figure 16.  $t_{LOOP1}$  vs Free-Air Temperature

## Timing Test Information

Figure 17. Test Diagram

Figure 18.  $t_{Loop1}$  Setup and Timing Diagram

Figure 19. Common-Mode Transient Immunity Test Circuit

## Applications Information

### Overview

The inter-integrated circuit (I<sup>2</sup>C) bus is a single-ended, two wire bus for efficient inter-IC communication and is used in a wide range of applications. The I<sup>2</sup>C bus is used for communication between multiple masters or a single master and slaves. The master device controls the serial clock line (SCL), and data is bidirectional transferred on the serial data line (SDA) between master and slaves. The I<sup>2</sup>C bus can theoretically add up to 112 communication nodes, however, the number of nodes will increase the load capacitance on the bus, thereby limiting the communication distances and communication speeds. In applications, tradeoffs are often made between communication speeds, bus length, and number of nodes based on actual conditions.

The I<sup>2</sup>C bus supports data transmission in four speeds: standard mode (up to 100Kbps), fast mode (up to 400Kbps), fast mode plus (up to 1Mbps), and high-speed mode (up to 3.4Mbps). The SI8600AC-B-IS device support all the above four communication modes.

### Functional Description

The SI8600AC-B-IS device is low-power bidirectional isolators compatible with the I<sup>2</sup>C interface.

This device have logic input and output buffers that are separated by using a silicon dioxide ( $\text{SiO}_2$ ) barrier. This device block high voltages and prevent noise currents from entering the control side ground, avoiding circuit interference, and damaging sensitive components.

Each channel output of the SI8600AC-B-IS device is made open-drain to comply with the open-drain technology of I<sup>2</sup>C. Serial data line (SDA) and serial clock line (SCL) need to add pull-up resistors to ensure normal operation of the system. It is recommended that side 1 of the I<sup>2</sup>C isolator be connected to the processor and sides 2 to the bus when there are multiple nodes on the I<sup>2</sup>C bus as side 2 support up to 400pF capacitance load.

The SI8600AC-B-IS device feature two bidirectional channels that have open-drain outputs, As shown in Figure 20. As a logic low on one side causes the corresponding pin on the other side to be pulled low, to avoid data-latching within the device, The output logic low ( $V_{OL1}$ ) voltages of SDA<sub>1</sub> and SCL<sub>1</sub> are at least 60mV higher than the input threshold high ( $V_{IHT1}$ ) of SDA<sub>1</sub> and SCL<sub>1</sub>, As shown in Figure 21.

Because the Side 2 logic levels/thresholds are standard I<sup>2</sup>C values, multiple SI8600AC-B-IS devices connected to a bus by their Side 2 pins can communicate with each other and with other I<sup>2</sup>C compatible devices. However, because the Side 1 pin has a modified output level/ input threshold, this side of the SI8600AC-B-IS can communicate only with devices that conform to the I<sup>2</sup>C standard.

The output low voltages of SI8600AC-B-IS device is guaranteed for sink currents of up to 35mA for side 2, and 3.5mA for side 1.

To enhance system reliability, it is recommended to connect the node with larger load capacitance and longer wires on side 2 for point-to-point communication.

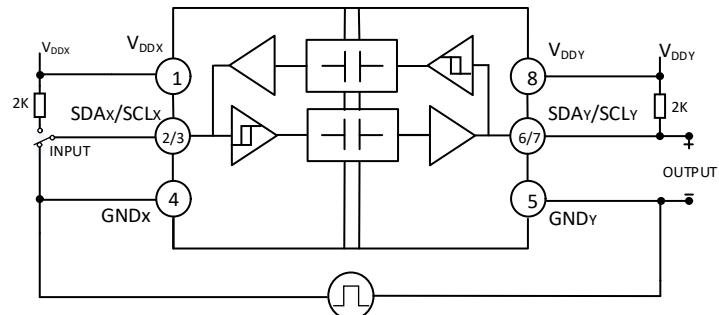

### Typical Application Diagram

Figure 22 shows a typical application circuit including the pull-up resistors required for both Side 1 and Side 2. Bypass capacitors with values from 0.1µF to 10µF are required between VDD1 and GND1 and between VDD2 and GND2. To enhance the robustness of a design, the user may connect a resistor (50-200Ω) in series between R2 and C1 and between R3 and C2 if the system is excessively noisy.

Figure 22. Typical Isolated I<sup>2</sup>C Interface Using the SI8600AC-B-IS

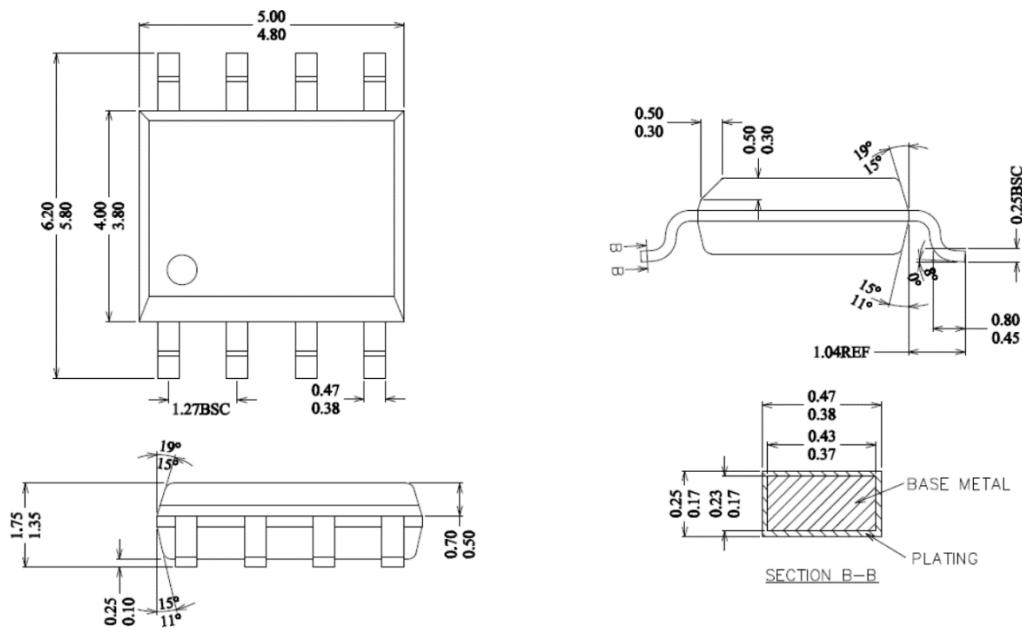

## Outline Dimensions

NOTES:

ALL DIMENSIONS REFER TO JEDEC STANDARD MS-012 AA

DO NOT INCLUDE MOLD FLASH OR PROTRUSION.

Figure 23. 8-Lead SOP Outline Package-dimension unit(mm)

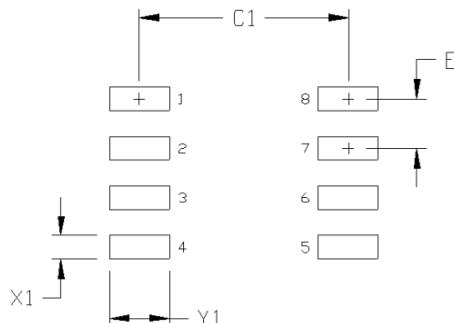

Figure 24.8-Lead SOP Land Pattern

Table 12.8-Lead SOP Land Pattern Dimensions

| Dimension | Feature            | Parameter | Unit |

|-----------|--------------------|-----------|------|

| C1        | Pad column spacing | 5.40      | mm   |

| E         | Pad row pitch      | 1.27      | mm   |

| X1        | Pad width          | 0.60      | mm   |

| Y1        | Pad length         | 1.55      | mm   |

Note:

1. This land pattern design is based on IPC -7351.

2. All feature sizes shown are at maximum material condition and a card fabrication tolerance of 0.05 mm is assumed.

### Attention

- Any and all HUA XUAN YANG ELECTRONICS products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your HUA XUAN YANG ELECTRONICS representative nearest you before using any HUA XUAN YANG ELECTRONICS products described or contained herein in such applications.

- HUA XUAN YANG ELECTRONICS assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all HUA XUAN YANG ELECTRONICS products described or contained herein.

- Specifications of any and all HUA XUAN YANG ELECTRONICS products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

- HUA XUAN YANG ELECTRONICS CO.,LTD. strives to supply high-quality high-reliability products. However, any and all semiconductor products fail with some probability. It is possible that these probabilistic failures could give rise to accidents or events that could endanger human lives, that could give rise to smoke or fire, or that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any or all HUA XUAN YANG ELECTRONICS products(including technical data, services) described or contained herein are controlled under any of applicable local export control laws and regulations, such products must not be exported without obtaining the export license from the authorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written permission of HUA XUAN YANG ELECTRONICS CO.,LTD.

- Information (including circuit diagrams and circuit parameters) herein is for example only ; it is not guaranteed for volume production. HUA XUAN YANG ELECTRONICS believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the HUA XUAN YANG ELECTRONICS product that you intend to use.