#### **Descriptions**

WAS4644C-36/TR is a high performancefour-data lane MIPI, D-PHY or threedata lane MIPI, C-PHY switch. This single-poledoublethrow (SPDT) switch isoptimized for switching between two high-speed or low-power MIPI sources.

The WAS4644C-36/TR has wide bandwidth and maintains good signal integrity, which makes it ideal is designed for the MIPI specification and allows connection to a CSI or DS Imodule.

36 Ball Wafer Level Chip Scale Package (CSP) 2.4mmx2.4mm with Pb-free and Halogen-free, makes it ideal for mobile device.

#### **Order Information**

| Package           |               | Part Number    | Top-Side Marking |

|-------------------|---------------|----------------|------------------|

| CSP-36(WLCSP-36B) | Tape and Reel | WAS4644C-36/TR | A644             |

#### **Features**

- Pin-to-Pin FSA644, CSP-36(WLCSP-36B)

- Signal Types: MIPI D-PHY and C-PHY

- Wide VCC Supply Range: 1.65v~5.5v

- Low Quiescent Current: 28uA Typical when VCC=1.8V

- Insertion loss: -1dB@1GHz, -2dB@1.5GHz, -3dB@2.5GHz

- Channel-to-Channel Cross-talk: -30dB Typical

- Power-off Truly Isolated and Off-Isolation: -25dB Typical

## **Applications**

Laptop, Multi-Camera and Displays, 4G/5G Smart Phone, Mobile and Al Device

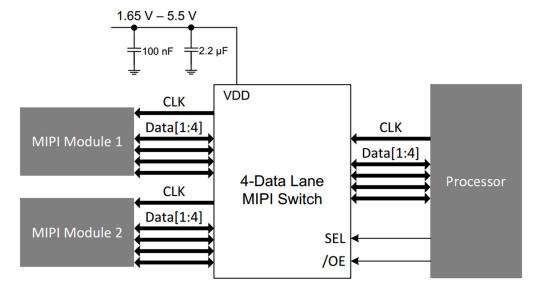

#### **Functional Diagram**

Fig.1 Functional Diagram

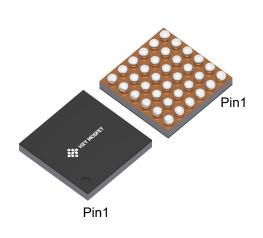

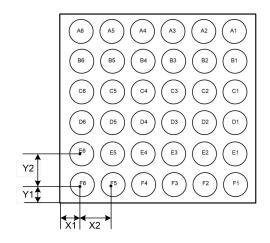

## **Pin Configuration**

#### **Top Through View** DA2N Α В DA3N С D NC CLKBN Ε DB4N DB2N DB2P F 2 5 6

Fig.2 Top-Through View and Top-Side View

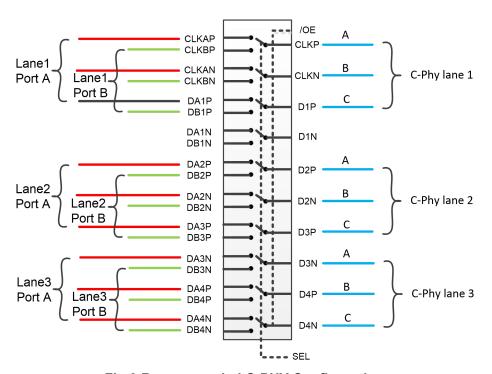

Fig.3 Recommended C-PHY Configuration

## **Pin Descriptions**

| Pin | Scriptions | Type | December 2                                                               |  |  |

|-----|------------|------|--------------------------------------------------------------------------|--|--|

| #   | Name       |      | Description                                                              |  |  |

| A1  | CLKN       | I/O  | Common Side Clock Path Negative                                          |  |  |

| A2  | CLKP       | I/O  | Common Side Clock Path Positive                                          |  |  |

| A3  | CLKAP      | I/O  | A Side Clock Path Positive                                               |  |  |

| A4  | DA1P       | I/O  | A Side Data Path 1 Positive                                              |  |  |

| A5  | DA2P       | I/O  | A Side Data Path 2 Positive                                              |  |  |

| A6  | DA2N       | I/O  | A Side Data Path 2 Negative                                              |  |  |

| B1  | D1N        | I/O  | Common Side Data Path 1 Negative                                         |  |  |

| B2  | D1P        | I/O  | Common Side Data Path 1 Positive                                         |  |  |

| В3  | CLKAN      | I/O  | A Side Clock Path Negative                                               |  |  |

| B4  | DA1N       | I/O  | A Side Data Path 1 Negative                                              |  |  |

| B5  | DA3P       | I/O  | A Side Data Path 3 Positive                                              |  |  |

| B6  | DA3N       | I/O  | A Side Data Path 3 Negative                                              |  |  |

| C1  | D2N        | I/O  | Common Side Data Path 2 Negative                                         |  |  |

| C2  | D2P        | I/O  | Common Side Data Path 2 Positive                                         |  |  |

| C3  | NC         | 0    | Not Connected                                                            |  |  |

| C4  | VCC        | PWR  | 1.5~5V Positive Supply                                                   |  |  |

| C5  | DA4P       | I/O  | A Side Data Path 4 Positive                                              |  |  |

| C6  | DA4N       | I/O  | A Side Data Path 4 Negative                                              |  |  |

| D1  | D3N        | I/O  | Common Side Data Path 3 Negative                                         |  |  |

| D2  | D3P        | I/O  | Common Side Data Path 3 Positive                                         |  |  |

| D3  | GND        | GND  | Primary Ground Connection. Must be Connected to System Ground            |  |  |

| D4  | NC         | 0    | Not Connected                                                            |  |  |

| D5  | CLKBN      | I/O  | B Side Clock Path Negative                                               |  |  |

| D6  | CLKBP      | I/O  | B Side Clock Path Positive                                               |  |  |

| E1  | D4N        | I/O  | Common Side Data Path 4 Negative                                         |  |  |

| E2  | D4P        | I/O  | Common Side Data Path 4 Positive                                         |  |  |

| E3  | DB4P       | I/O  | B Side Data Path 4 Positive                                              |  |  |

| E4  | DB3P       | I/O  | B Side Data Path 3 Positive                                              |  |  |

| E5  | DB1N       | I/O  | B Side Data Path 1 Negative                                              |  |  |

| E6  | DB1P       | I/O  | B Side Data Path 1 Positive                                              |  |  |

| F1  | _OE        | I    | Chip Enable, Low Active                                                  |  |  |

| F2  | SEL        | I    | Channel Selection. When Low, A side selected; When High, B side selected |  |  |

| F3  | DB4N       | I/O  | B Side Data Path 4 Negative                                              |  |  |

| F4  | DB3N       | I/O  | B Side Data Path 3 Negative                                              |  |  |

| F5  | DA2N       | I/O  | A Side Data Path 2 Negative                                              |  |  |

| F6  | DA2P       | I/O  | A Side Data Path 2 Positive                                              |  |  |

**Table-1 Pin Descriptions**

# **Absolute Maximum Ratings** over operating free-air temperature range (unless otherwise noted) (1)

|                       |                 | Range      | Unit |

|-----------------------|-----------------|------------|------|

| Power Supply Voltage  | VCC             | -0.5 ~ 6.0 | V    |

| Control Pins          | _OE, SEL        | -0.5 ~ VCC | V    |

| DC Switch I/O Voltage | V <sub>SW</sub> | -0.3 ~ VCC | V    |

| DC I/O Current        | l <sub>IK</sub> | -50 ~ 50   | mA   |

| Storage Temperature   | т               | -55 ~ 150  | °C   |

| Range                 | $T_{STG}$       | -55 ~ 150  | 30   |

| ESD HBM,              | VCC             | ±2         | kV   |

| ANSI/ESDA/JEDEC       | _OE, SEL        | ±2         | kV   |

| JS-001-2012           | Other I/O Pins  | ±2         | kV   |

|                       | VCC             | ±200       | V    |

| ESD MM, JESD22-A115   | _OE, SEL        | ±2         | kV   |

|                       | Other I/O Pins  | ±2         | kV   |

#### **Table-2 Absolute Maximum Ratings**

## **Recommend Operating Conditions**

|                       |                | Range      | Unit |

|-----------------------|----------------|------------|------|

| Power Supply Voltage  | VCC            | 1.65 ~ 5.5 | V    |

| Control Pins          | _OE, SEL       | 0 ~ VCC    | V    |

| Signal Pins           | HS Mode        | 0 ~ 0.3    | V    |

|                       | LP Mode        | 0 ~ 1.3    | V    |

| Operating Temperature | T <sub>A</sub> | -40 ~ 85   | °C   |

#### **Table-3 Recommend Operating Conditions**

<sup>(1)</sup> Stresses beyond those listed in Table-2 *Absolute Maximum Ratings* may cause permanent damage to the device. They are stress ratings only, which do not imply functional operation of the device at these or any other conditions. Beyond those indicated under *Recommended Operating Conditions*, exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

<sup>(1)</sup> If \_OE is left undriven, it will be pulled up to VCC by internal resistor; If SEL is left undriven, it will be pulled down to Ground by internal resistor.

## Electrical Characteristics (Ta=25°C, VCC=1.8V, unless otherwise specified)

| Parameter                                 | Symbol               | Conditions                                                                           | Min. | Typ. | Max. | Unit |

|-------------------------------------------|----------------------|--------------------------------------------------------------------------------------|------|------|------|------|

| Power Supply                              |                      |                                                                                      |      |      |      |      |

| VCC Quiescent Current                     | IQ                   | SEL=0 or VCC, _OE=0                                                                  |      | 28   |      | uA   |

| Power-down Current                        | I <sub>PD</sub>      | SEL=0 or VCC, _OE=VCC                                                                |      |      | 1    | uA   |

| DC Characteristics                        | 1                    |                                                                                      |      | ı    | 1    |      |

| Input logic high                          | V <sub>IH</sub>      | VCC=1.8~4.5V                                                                         | 1.6  |      |      | V    |

| Input logic low                           | V <sub>IL</sub>      | VCC=1.8~4.5V                                                                         |      |      | 0.4  | V    |

| _OE Internal pull-up resistor             | R <sub>UP</sub>      |                                                                                      |      | 2    |      | МΩ   |

| SEL Internal pull-down resistor           | R <sub>DN</sub>      |                                                                                      |      | 2    |      | МΩ   |

| On-Resistance for LP MIPI                 | R <sub>ON_LP</sub>   | V <sub>IS</sub> = 1.2V I <sub>ON</sub> =8mA                                          |      | 7.5  | 9    | Ω    |

| On-Resistance for HS MIPI                 | R <sub>ON_HS</sub>   | V <sub>IS</sub> = 0.2V I <sub>ON</sub> =8mA                                          |      | 6.7  | 8    | Ω    |

| R <sub>ON</sub> Flatness for LP MIPI      | R <sub>FLAT_LP</sub> | V <sub>IS</sub> = 0 to 1.2V I <sub>ON</sub> =8mA                                     |      | 0.8  | 1    | Ω    |

| R <sub>ON</sub> Flatness for HS MIPI      | R <sub>FLAT_LP</sub> | V <sub>IS</sub> = 0 to 0.2V I <sub>ON</sub> =8mA                                     |      | 0.2  | 0.3  | Ω    |

| R <sub>ON</sub> Matching Between Channels | R <sub>MATCH</sub>   | V <sub>IS</sub> = 0 to 1.2V I <sub>ON</sub> =8mA                                     |      | 0.1  |      | Ω    |

| Switch Off Leakage Current                | loff                 | _OE=VCC Dn, Dp =VCC DAn, DBn, DAp, DBp=0 CLKn, CLKp=0 CLKAn, CLKBn, CLKAp, CLKBp=VCC | -0.5 |      | 0.5  | uA   |

| AC Characteristics                        | 1                    | I                                                                                    | ı    |      | 1    | I    |

| Enable Time _OE to Output                 | t <sub>EN</sub>      | R <sub>L</sub> =50Ω C <sub>L</sub> =0pF V <sub>IS</sub> = 0.6V                       |      | 80   | 150  | uS   |

| Disable Time _OE to Output                | t <sub>DIS</sub>     | R <sub>L</sub> =50Ω C <sub>L</sub> =0pF V <sub>IS</sub> = 0.6V                       |      | 40   | 250  | nS   |

| Turn-On Time SEL to Output                | ton                  | R <sub>L</sub> =50Ω C <sub>L</sub> =0pF V <sub>IS</sub> = 0.6V                       |      | 400  | 1200 | nS   |

| Turn-Off Time SEL to Output               | t <sub>OFF</sub>     | $R_L=50\Omega$ $C_L=0pF$ $V_{IS}=0.6V$                                               |      | 130  | 800  | nS   |

| Break-Before-Make Time                    | t <sub>BBM</sub>     | R <sub>L</sub> =50Ω C <sub>L</sub> =0pF V <sub>IS</sub> = 0.6V                       |      | 250  | 500  | nS   |

| Propagation Delay                         | t <sub>PD</sub>      | R <sub>L</sub> =50Ω C <sub>L</sub> =0pF V <sub>IS</sub> = 0.6V                       |      | 0.25 |      | nS   |

| Off Isolation                             | Off                  | $R_L = 50\Omega$ f = 1.2GHz $V_{IS} = 0.2V_{PP}$                                     |      | -33  |      | dB   |

| Crosstalk (Channel-to-Channel)            | X <sub>TALK</sub>    | $R_L = 50\Omega$ f = 1.2GHz $V_{IS} = 0.2V_{PP}$                                     |      | -43  |      | dB   |

| -3dB Bandwidth (Insertion Loss)           | BW <sub>-3dB</sub>   | R <sub>L</sub> =50Ω C <sub>L</sub> =0pF Signal 0dBm                                  | 2.5  | 3.5  |      | GHz  |

| Capacitance                               |                      |                                                                                      |      |      |      |      |

| Switch On Capacitance                     | Con                  | V <sub>Bias</sub> = 0.2V, f = 1MHz                                                   |      | 1.5  |      | pF   |

| Switch Off Capacitance                    | C <sub>OFF</sub>     | V <sub>Bias</sub> = 0.2V, f = 1MHz                                                   |      | 1.0  |      | pF   |

**Table-4 Electrical Characteristics**

#### Note:

- (1) Flatness is defined as the difference between maximum and minimum value of ON-resistance at the specified analog signal voltage points.

- (2) R<sub>ON</sub> matching between channels is calculated by subtracting the channel with the lowest max Ron value from the channel with the highest max Ron value.

- (3) Crosstalk is inversely proportional to source impedance

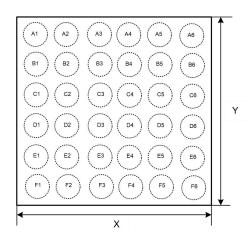

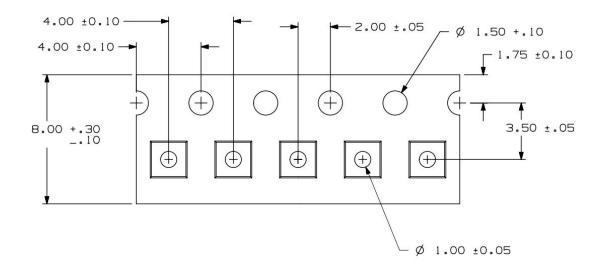

## **Package Outline Dimensions**

## CSP-36(WLCSP-36B)

**Bottom-Up View**

**Top-Through View**

Fig.3 Package Outline Dimensions

| Symbol |       | Dimensions In Millimeter |       |  |  |

|--------|-------|--------------------------|-------|--|--|

|        | Min.  | Тур.                     | Max.  |  |  |

| X      | 2.37  | 2.40                     | 2.43  |  |  |

| Υ      | 2.37  | 2.40                     | 2.43  |  |  |

| X1     |       | 0.16                     |       |  |  |

| X2     |       | 0.40                     |       |  |  |

| X3     | 0.175 | 0.205                    | 0.235 |  |  |

| Y1     |       | 0.16                     |       |  |  |

| Y2     |       | 0.40                     |       |  |  |

| Z      | 0.550 | 0.600                    | 0.650 |  |  |

| Z1     | 0.145 | 0.170                    | 0.195 |  |  |

| Z2     | 0.340 | 0.365                    | 0.390 |  |  |

| Z3     | 0.395 | 0.040                    | 0.045 |  |  |

**Table-5 Package Outline Dimensions**

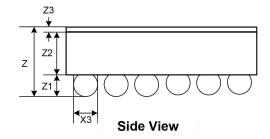

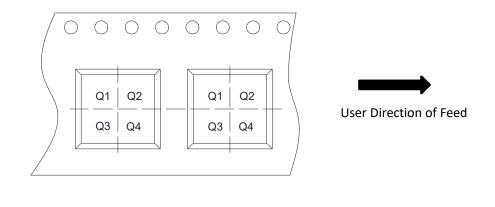

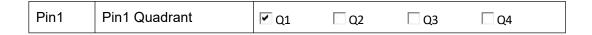

## **Tape and Reel Information**

# **Quadrant Assignments for PIN 1 Orientation In Tape**

Fig.4 Tape and Reel Information

#### **Attention**

- Any and all HUA XUAN YANG ELECTRONICS products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your HUA XUAN YANG ELECTRONICS representative nearest you before using any HUA XUAN YANG ELECTRONICS products described or contained herein in such applications.

- HUA XUAN YANG ELECTRONICS assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all HUA XUAN YANG ELECTRONICS products described or contained herein.

- Specifications of any and all HUA XUAN YANG ELECTRONICS products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

- HUA XUAN YANG ELECTRONICS CO.,LTD. strives to supply high-quality high-reliability products. However, any and all semiconductor products fail with some probability. It is possible that these probabilistic failures could give rise to accidents or events that could endanger human lives, that could give rise to smoke or fire, or that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any or all HUA XUAN YANG ELECTRONICS products(including technical data, services) described or contained herein are controlled under any of applicable local export control laws and regulations, such products must not be exported without obtaining the export license from the authorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written permission of HUA XUAN YANG ELECTRONICS CO.,LTD.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. HUA XUAN YANG ELECTRONICS believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the HUA XUAN YANG ELECTRONICS product that you intend to use.